Litrin的回答

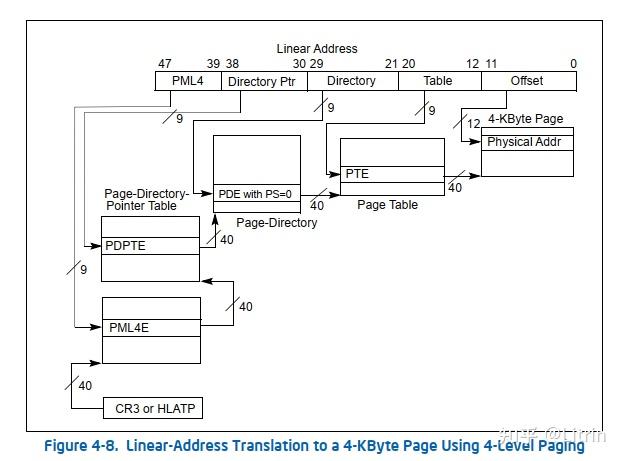

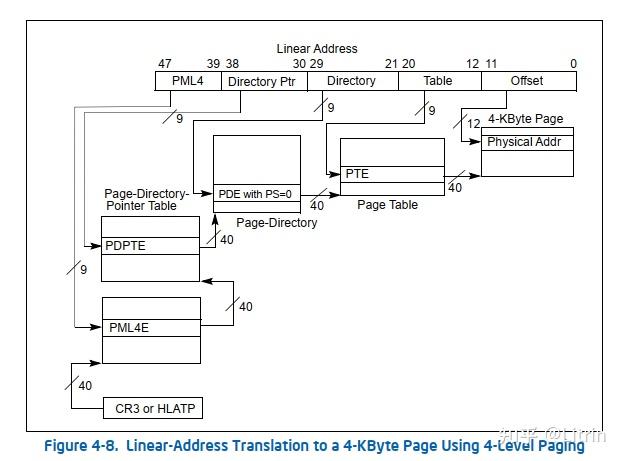

线性地址4K页表的4级映射逻辑

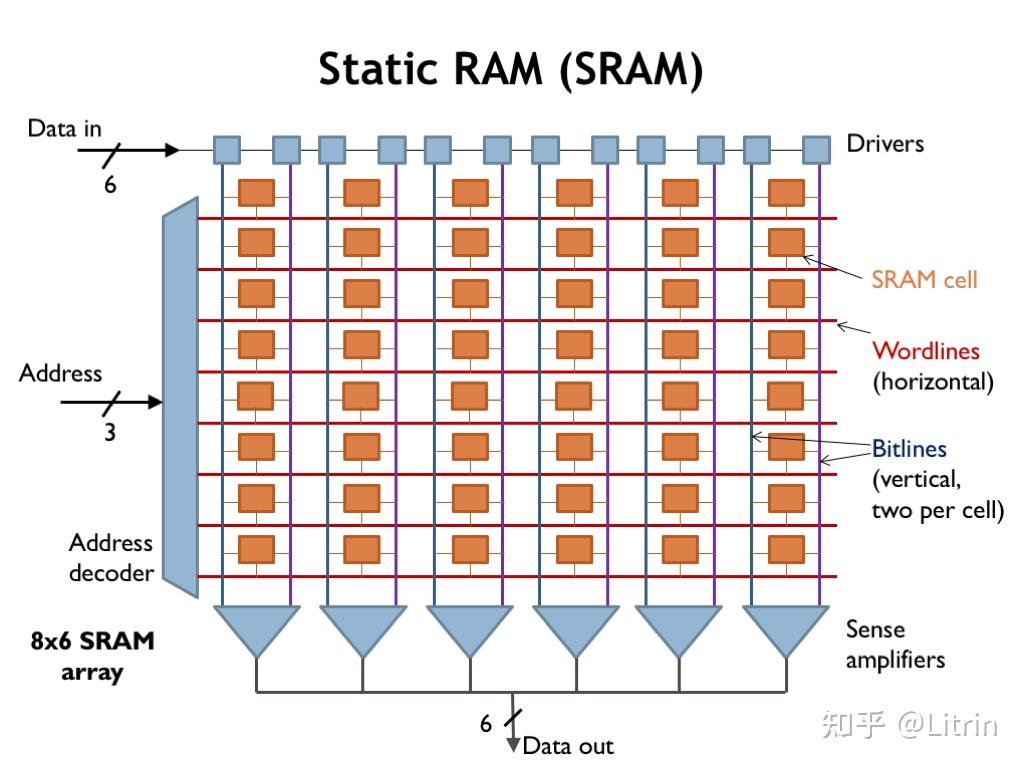

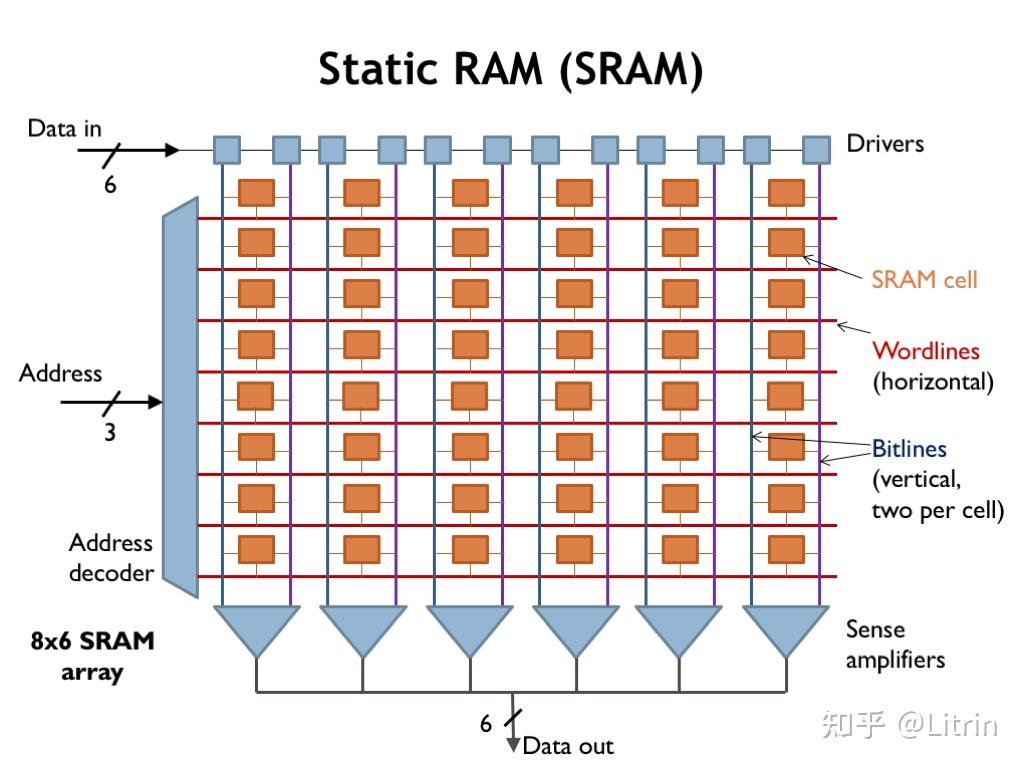

线性地址4K页表的4级映射逻辑 SRAM array,这个算不算二维寻址呢?

SRAM array,这个算不算二维寻址呢? MCR DIMMs are able to simultaneously operate two ranks and deliver 128bytes to a CPU (64 bytes from each rank) roughly doubling the performance per DIMM. The MCR DIMM utilizes a data buffer on the modules to help combine transfers from each rank.

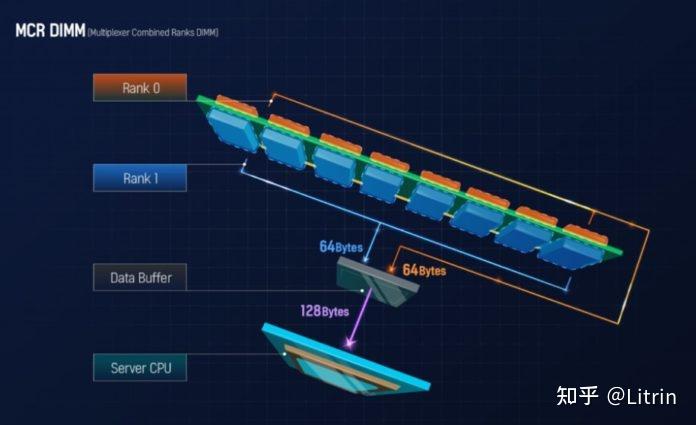

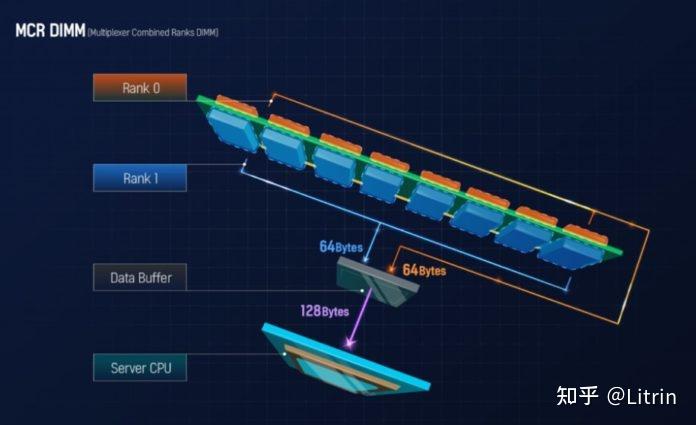

MCR DIMMs are able to simultaneously operate two ranks and deliver 128bytes to a CPU (64 bytes from each rank) roughly doubling the performance per DIMM. The MCR DIMM utilizes a data buffer on the modules to help combine transfers from each rank.

从某种角度上看,一旦你觉得自己有了新的idea,绝大多数情况下只能说明你对业界了解的不够深……

到芯片半导体这边实属是典范了。现实中的高性能芯片的设计和实现逻辑上已经到了无所不用其极的状态了。

首先“内存中的实际布局是将一列数据连续放置在内存中”本身这个就是软件开发层面上的逻辑,而从OS对内存的管理上讲,数据是分页管理的,特别是日常环境中,逻辑上的连续,到物理上并不一定就是连续的。接下来就是多通道内存已经够普及了吧,即便是真正意义上连续的数据,到了内存控制器或者内存介质这一层有会被分配到不同的控制器,不同的介质bank上。

线性地址4K页表的4级映射逻辑

线性地址4K页表的4级映射逻辑内存介质的存储方式又是分了一层rank,下边还有列column和行row,到这里还只是为了寻址方便,光从逻辑上分这就有了远远不止一个维度的交叉寻址了。再从实现的角度上看内存条还会有多个芯片分摊位宽这种骚操作,而且还会有具体工艺上的电路堆叠技术……

SRAM array,这个算不算二维寻址呢?

SRAM array,这个算不算二维寻址呢?而事实上CPU通过CHA发送内存访问请求,现阶段CHA设计早就趋向于通过一致性哈希算法实现的多路分布式系统,所有的CHA独立且相对均衡地访问所有内存空间范围内的地址。

以上,如果这都不能算是多维度交叉寻址的话,那抱歉我要祭出MCR内存的实现方法了。从软件设计的角度上看这已经不是在二分法交叉寻址上做优化了——请求分发+多路并行的思路属于软件负载均衡范式,眼看着就要被逼着上生产者-消费者设计模式分布式寻址了。

MCR DIMMs are able to simultaneously operate two ranks and deliver 128bytes to a CPU (64 bytes from each rank) roughly doubling the performance per DIMM. The MCR DIMM utilizes a data buffer on the modules to help combine transfers from each rank.

MCR DIMMs are able to simultaneously operate two ranks and deliver 128bytes to a CPU (64 bytes from each rank) roughly doubling the performance per DIMM. The MCR DIMM utilizes a data buffer on the modules to help combine transfers from each rank.附送一段散装工地英语发音方法练习,想象一下在一个到处都是高速风扇和大功率空调送风的机房里debug时,为了抓住转瞬即逝的状态需要你快速且清晰的吼出一句:“On hold! Randomly adopt a block on a blank rank of that bank! ~thanks!”

update 20240617盗了几张图,方便大家理解(凑齐3张图片)

- Guide P. Intel® 64 and ia-32 architectures software developer’s manual[J]. Volume 3A: System programming Guide, Part, 2024, 4(5): 4-20.

- 14.1 Annotated Slides | Computation Structures | Electrical Engineering and Computer Science | MIT OpenCourseWare

- What is a MCR DIMM or Multiplexer Combined Ranks DIMM

相关内容